柴田 貴康 Takayasu Shibata

●エフィニックスFPGA

エフィニックスは2012年に米国で設立されたFPGAベンダです.AMD,SAMSUNG Venture Investment,Malaysia Venture Capital Management Berhad (MAVCAP),AIM,Alibaba,Hong Kong X-Techなどが出資しているようです.FPGAを持つAMDが投資しているところが興味深いところです.ミドルクラス以下をエフィニックス,ミドルクラス以上をAMDといったようにターゲットを分けるのかもしれません.

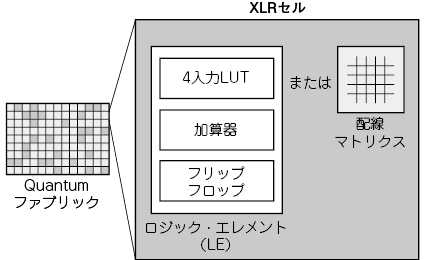

●Quantumアーキテクチャ

一般的なFPGAは,論理ブロックをつなぎ替えるための配線スイッチがあらかじめ敷かれています.エフィニックスのFPGAは,論理ブロックとしても,配線マトリクスとしても使用できるXLRセルを持つことが特徴です(図1).XLRセルはタイル状に敷き詰められており,ロジックかルーティングかは開発ソフトウェアによって最適化されます.

第1世代の40nmの通常CMOSプロセスで生産されるTrionシリーズの場合,従来のFPGAに比べ2~4倍の面積を削減し,消費電力は1/2になるとのことです.

●FPGAのラインアップ

100万個以上の論理ブロック(ロジック・エレメント)を持つFPGAがラインアップされています.16nmプロセスで生産されるTitaniumシリーズは,専用の高速DSPブロックや高度に構成可能なメモリ・ブロックを持っています.第1世代に比べ動作周波数は3倍になり,効率は2倍向上しているとのことです.

●Trionシリーズ

Trionは4000~約11万のロジック・エレメント(LE)を持つファミリです.GPIO,PLL,発振器,MIPI,DDR3/LPDDR3/LPDDR2,LVDSなどのインターフェースを備えています.製造プロセスは40nmです.

約1.3万LEより大規模の品種はCSI-2コントローラを内蔵した4レーン対応のMIPIのDPHYを持っており,カメラ画像の取り込みや出力などの画像処理も行いやすくなっています.

パッケージは49~576ピンのBGA以外にQFPもあるので自作派にも使いやすいと思います.

●Titaniumシリーズ

Titaniumは,約3.6万~約97万のロジック・エレメントを持つファミリです.Trionにも装備されているインターフェースに加え,高速SerDesやPCI Express Gen4を備えています.16nmプロセスで製造されています.

パッケージは,64~1156ピンのBGAです.約6.2万LE以下の品種には,HyperRAM,フラッシュ・メモリを内蔵した100ピンのBGAパッケージがあります.約18万LEの品種には,LPDDR4メモリを内蔵した484ピンのBGAパッケージがあります.

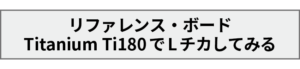

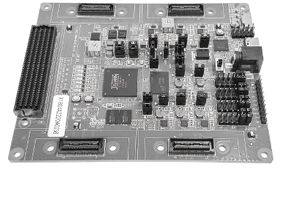

開発ボードのTitanium Ti180 M484 Development Kitを使用して,LEDの点滅を行います(写真1).

開発ボードの主な仕様を表1に示します.回路図は,ウェブ・ページの「サポート」-「Documentation」のページからダウンロード可能です.

https://www.efinixinc.com/jp/index.html

一部,ユーザまたはボードの登録が必要な場合もありますが,PCBレイアウト(ガーバ・データ)もウェブ・ページからダウンロード可能です.カメラやネットワーク機能を持つオプションのボードもそろっています.

Titanium Ti180については次のウェブ・ページも参照してください.

| 要素 | 仕様 |

| FPGA | Ti180M484I3(エフィニックス) 484BGAパッケージ |

| RAM | LPDDR4 SDRAM,256Mビット |

| フラッシュ・メモリ | 256MビットSPI,NOR型 |

| I/O | 4×MIPI,LVDS,GPIO高速QSEコネクタ, microSDカード・スロット,メザニン・カード・スロット,USB Type-Cコネクタ |

| その他 | PLL入力用発振器 (25MHz,33.33MHz,50MHz,74.25MHz), ユーザLED×6,押しボタン・スイッチ×2 |

開発用ソフトウェアとしてEfinityが用意されています.GUIとコマンドライン・スクリプトによる開発の両方をサポートしています.記述言語はVerilog HDL,SystemVerilog,VHDLが使えます.

ロジック制約やピン配置を行うためのインターフェース・デザイナや,IPコアを選択するIPマネージャ,ロジックや配線を表示するフロアプラン・ビューアやタイミング制約や参照を行うタイミング・ブラウザも備わっています.

▶ハード・コンポーネントの扱い方

Efinityの特徴として,FPGAの開発ブロックを論理回路部分とハード・コンポーネント部分とに分けて考えることが挙げられます.

ハード・コンポーネントはインターフェース・デザイナで全ての設定を行います.対象はPLLやDRAMコントローラ,I/O各種,MIPIなどの高速インターフェースなど論理以外のハードウェア全てです.

設定したハード・コンポーネントは論理回路のRTLコードから接続して使用するような構成になります.

これにより論理回路(RTL)部分と,それぞれのFPGAの持っているハード・マクロとを明確に分けて開発することができ,移植性やデバイス構成の柔軟性が向上します.

▶シミュレータは外部ツールを使う

RTLシミュレータは含まれていません.オープンソースのシミュレータ(iverilogやverilator)などを別途用意する必要があります.

各デバイスごとのプリミティブ(コンポーネント)のシミュレーション・モデルはEfinityにバンドルされているので,ModelSimなど市販のシミュレータも使用可能です.

他にも,作成した回路をピンに割り当てたり,グラフィカルに表示したりするパッケージ・プランナや,ロジック・アナライザ機能と仮想I/Oデバッグ機能を備えたハードウェア・デバッガ,FPGAへ回路情報(ビットストリーム)を転送するプログラマを備えています.

Efinityは無料ですが,ダウンロードするにはアカウント登録が必要です.開発対象のデバイスには制限はありません.

●ダウンロードとインストール

▶ユーザ登録

ユーザ登録するため,Registerページ(1)にアクセスし,各項目を入力します.

”Are you working with a distributor or reseller?”との質問の答えは,アマチュアならDigi-KeyかOtherを選択すればよいでしょう.

”How experienced are you with FPGAs?”という質問には,初心者ならNovice,経験者ならExperiencedやPower userを選択します.

項目を入力したら「Register」をクリックします.登録したメール・アドレスにアカウント確認メールが届くので,掲載されているURLを開くと登録完了です.

▶開発ボードの登録

Register a Development Kitのページ(2)にアクセスします.開発ボードとシリアル番号および購入先を入力し,「Register My Kit」をクリックします.

”Development Kit Registration Successful”と表示されたら登録完了です.

現在では,ユーザ登録すれば,ボードがない場合でも無償ライセンスをリクエストできます.

▶Efinityのダウンロード

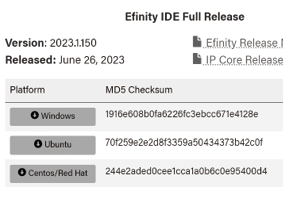

ダウンロードは,Support Center(3)で「Download Software」を選択します.使用するOSに合わせてEfinity IDE v2023.1.150(2023年8月時点での最新版)を選択します(図2).

ライセンスについてのページが表示されるので内容を確認して問題なければ,「I agree」を選択します.自動的にダウンロードが開始されます.

▶インストール

ダウンロードしたファイルをダブルクリックします.

efinity-2023.1.150-windows-x64.msi

インストーラが起動するので,「Next」をクリックします.End-User License Agreement画面が開くので,「I accept the terms in the License Agreement」にチェックを入れ,「Next」をクリックします.

Destination Folder画面が開きます.デフォルトのままで,「Next」をクリックします.

Ready to install Efinity 2023.1画面が開くので,「Install」をクリックします.

“このアプリがデバイスに変更を加えることを許可しますか?”と聞かれるので「はい」をクリックすると,インストールが実行されます.完了画面が表示されたら「Finish」をクリックします.

●Verilogで回路を設計

LED点滅(Lチカ)を行います.クロック入力33MHzを分周し,LEDを0.5秒点灯させた後,0.5秒消灯させます.クロックを分周し,16,500,000クロックごとにLEDを反転させます.

・Lチカの回路

RTLコードを,C:\FPGA\EFINIX\LED\RTLにled.vという名前で作成します(リスト1).

// LED Brink 0.5sec ON, 0.5sec OFF

// EFINIX Trion Ti180 M484 Development Kit

// RTL

// @shibatchii

// 2023/01/22

`timescale 1ns/1ps

module led(

clock,

nreset,

o_led

);

// 33.333333MHz/2=16.666666MHz=FE502Ah

parameter P_DIV = 24'hFE5029;

input clock; // clock 33.333333MHz

input nreset; // negative reset

output o_led; // led 0.5sec on 0.5sec off

reg [23:0] r_count;

reg r_led;

// Count 16,500,000

always @(posedge clock or negedge nreset) begin

if(nreset == 1'b0)

r_count[23:0] <= 24'h00_0000;

else

if(r_count[23:0] == P_DIV)

r_count[23:0] <= 24'h00_0000;

else

r_count[23:0] <= r_count[23:0] +

24'h00_0001;

end //

// toggle led

always @(posedge clock or negedge nreset) begin

if(nreset == 1'b0)

r_led <= 1'b0;

else

if(r_count[23:0] == P_DIV)

r_led <= ~r_led;

else

r_led <= r_led;

end //

assign o_led = r_led;

endmodule //・テストベンチ

C:\FPGA\EFINIX\LED\TESTBENCH にT_led.vという名前でテストベンチを,作成します(リスト2).

// LED Brink 0.5sec ON, 0.5sec OFF

// EFINIX Trion Ti180 M484 Development Kit

// Testbench

// @shibatchii

// 2023/01/22

`timescale 1ns/1ps

module T_led;

initial begin

$dumpvars();

end //

reg clock; // clock 33MHz

reg nreset; // negative reset

wire o_led; // led 0.5sec on 0.5sec off

led led (

.clock (clock ), // I clock 33MHz

.nreset (nreset ), // I negative reset

.o_led (o_led ) // O led 0.5sec on 0.5sec off

);

initial begin

forever begin

clock = 1'b0;

#15;

clock = 1'b1;

#15;

end //

end //

initial begin

nreset = 1'b0;

repeat(2)@(negedge(clock));

nreset = 1'b1;

repeat(70000000)@(posedge(clock));

$finish;

end //

endmoduler_count[23:0]で1650万クロック(0.5秒)カウントすると,また0からカウントし始めます.r_ledは,1650万クロックごとに反転します.

ledをインスタンスし,30nsのクロックを生成し接続しています.リセット後,1秒の2周期強の時間である7000万クロックが過ぎるとシミュレーションを停止します.

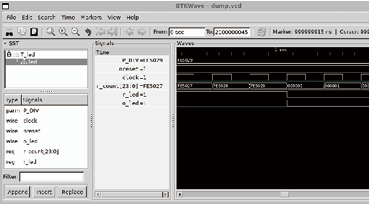

・シミュレータでチェック

Efinityにはシミュレータが付属していないので,WSL2のUbuntu上でiverilogとgtkwaveを使用してシミュレーションを行いました.正しく0.5秒ごとに反転していることが分かります(図3).

●ピンの割り当てを決める

最初にピン割り当てを決定しておきます.ボード上に6個あるLEDの中からLED2を使用します.サポート・ページからボードの回路図(Titanium Ti180 M484 Development Board Schematics and BOM)をダウンロードして回路を確認します.信号とピンの対応を表2に示します.

SW2は回路のリセット・ボタンとして使います.

| RTL 信号名 | ボードの 信号名 | FPGA 端子名 | 信号の意味 (接続するデバイス) |

| clock | GPIOL_32_PLLIN1 | K17 | 33MHzクロック |

| nreset | CRESET_N | D2 | 負論理リセット(SW2) |

| o_led | GPIOB_N_02_CSO | E1 | LED出力(LED2) |

●合成とフィッティング

論理合成のために制約ファイルを作ります.制約ファイルにはFPGA端子に対する入力や出力の遅延値,クロック周期を設定します.今回はクロック周期だけ設定します.

create_clock -name { clk33m } -period

30.000 [get_ports { clock }]clk33mは,クロックの定義名です.分かりやすい名前にします.30.000はクロック周期です(単位はns).get_portsでRTLで記述した端子のクロック名clockを指定します.

これをC:\FPGA\EFINIX\LED\SDCにled.sdcという名前で保存します.

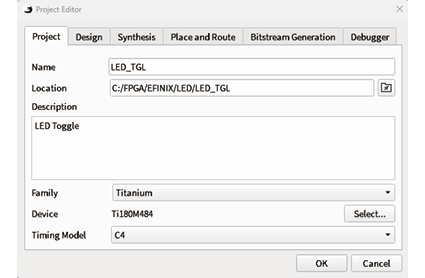

論理合成とフィッティングを行います.Efinity 2023.1を起動し,プロジェクトを作成するために「File」-「Create Project」を選択し,Project Editorを開きます.

▶プロジェクトの設定

・Projectタブ

Name欄には,プロジェクト名を設定します.ここではLED_TGLとしました.

Description欄には,LED Toggleと入力します.

Location欄にはプロジェクトの場所としてC:\FPGA\EFINIX\LED\LED_TGLを指定します.

Familyの中から,Titaniumを選択します.DeviceとしてTi180M484を,Timing ModelとしてC4を選択します(図4).

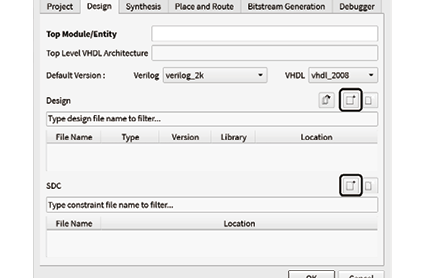

・Designタブ

「Design」タブを開き,「Add design file」をクリックします.設計制約ファイルの選択画面(図5)が開くのでデザインには設計ファイルのC:\FPGA\EFINIX\LED\RTLのled.vを選択し,「Open」をクリックします.

Top Module/Entity欄に,RTLのmodule名としてledと入力します.

制約ファイルはSDCの「Add SDC file」をクリックします(図5).

C:\FPGA\EFINIX\LED\SDCのled.sdcを選択し「Open」をクリックすると,設定した値が反映されます.

「OK」をクリックしProject Editorを閉じます.

▶ピンの割り当てを行う

論理合成とフィッティングを行います.「Flow」-「Synthesize」を選択するか,「シンセサイズ」アイコンをクリックします.

結果を見るとInterfaceでUnassigned Core Pins 3が赤文字で表示されています.これはピン割り当てを行っていないからです.

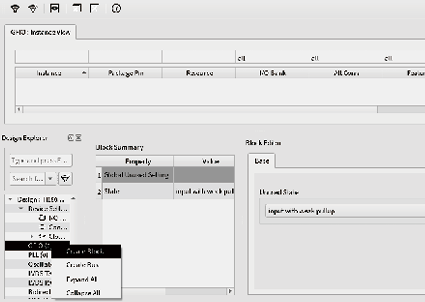

Efinityのピン割り当ての方法は独特です.他のFPGAツールになれた方はちょっと戸惑うかもしれません.ツール・バーから「Tools」-「Open Interface Designer」を選択するとEfinity Interface Designerが立ち上がります.

Design ExplorerのGPIO(0)を選択し,右クリックして「Create Block」を選択します.次に「Design」-「Show/ Hide GPIO Resouce Assigner」を開きます.もしくは左のアイコンからでも開けます.

GPIO:Instance Viewが開きます.

・GPIO(0)の設定

次にGPIO(0)を右クリックし「Create Block」を選択します(図6).

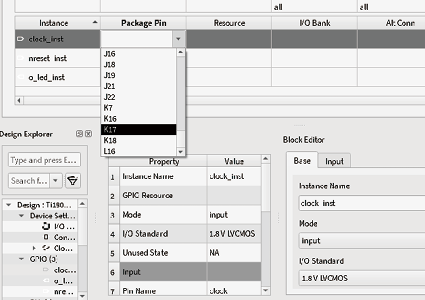

まずはclock入力の設定をします.Block EditorのBaseタブを選択します.Instance Name欄にclock_instと入力しEnterキーを押します.Modeを“input”に,I/O Standardを“1.8V LVCMOS”に設定します.

Inputタブを選択し,Pin NameをRTLと同じclockにします.それ以外はデフォルトのままにします.

・nresetの設定

GPIO(0)と同じようにnresetの設定をします.Instance Nameをnreset_instに,Pin Nameをnresetに,それ以外はGPIO(0)と同じ設定です.

・o_ledの設定

Instance Nameをo_led_instに,Modeをoutputに,I/O Standardを1.8V LVCMOSに設定します.Pin Nameはo_ledとし,それ以外はデフォルトのままとします.

画面中央付近にあるBlock Summaryの欄に設定した値が反映されます.

ピン割り当ての設定をします.GPIO:Instance Viewでclock_instのPackage Pinの箇所をダブルクリックします.ピン一覧がプルダウンされるので,K17ピンを選択します(図7).

選択すると各項目が自動的に入力されます.同じようにnreset_instをD2に,o_led_instをE1に割り当てます.

割り当て終えたら「Design」-「Check Design」をクリックします.問題があると結果が赤字で表示されます.問題なければ何も表示されません.

「Design」-「Generate Efinity Constraint Files」で設定ファイルを生成します.「File」-「Exit」でEfinity Interface Designerを閉じます.

もう一度Synthesizeから実行します.今度はInterfaceにエラーが表示されず終了します.ResultタブでTimingに問題がないこと(Slackがプラスになっている)を確認できます.

●開発ボード用USBドライバのインストール

開発ボードをPCに接続して使用するためには,Zadig 2.8(4)を使ってUSBドライバをインストールする必要があります.

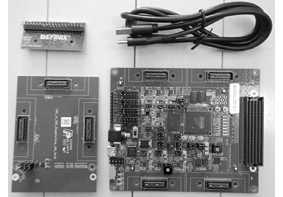

開発ボードを付属のUSBケーブルでPCに接続します.付属の電源アダプタを接続し,開発ボード上のスライド・スイッチを操作して電源を入れます(写真2).

ダウンロードしたzadig2.8.exeをダブルクリックして開きます.“このアプリがデバイスに変更を加えることを許可しますか?”と聞かれるので,「はい」を選択します.

Zadig update policyが開くので「Yes」を選択します.

Zadigが立ち上がるので,「Option」-「List All Devices」をクリックします.

プルダウンから「Ti180 M484 Development

kit (Interface 1)」を選択します.Ti180 M484 Development kit (Interface 0)はWindowsによって自動的にドライバがインストールされるので選択してはいけません.

Driverリストから「libusb-win32」を選択します.

「Replace Driver」ボタンをクリックするとインストールが開始されます.

”The driver was installed successfully.”と表示されたら完了です.「Close」をクリックしてZadigを閉じます.

●FPGAボードへの書き込みと動作確認

開発ボードにFPGAデータを書き込みます.「Tools」-「Open Programmer」とクリックすると,Efinity Programmerが開きます.

「Refresh USB Target」ボタンをクリックし,USB Target欄で「Titanium Ti180M484 Development Kit」を選択します.

次に「Select Image File」をクリックします.C:\FPGA\EFINIX\LED\LED_TGL\outflowにあるLED_TGL.bitを選択します.

「Start Program」ボタンをクリックすると,JTAGで書き込みが完了します.

ボードのLED2が1秒間隔で点滅します.SW3を押すとLED点滅回路にリセットがかかるため消灯します.離すとまた点滅を開始します.

❖参考文献❖

(2)Register a Development Kitのページ

しばた・たかやす @shibatchii

ピンバック: EFINIX FPGA | FPGAマガジン公式