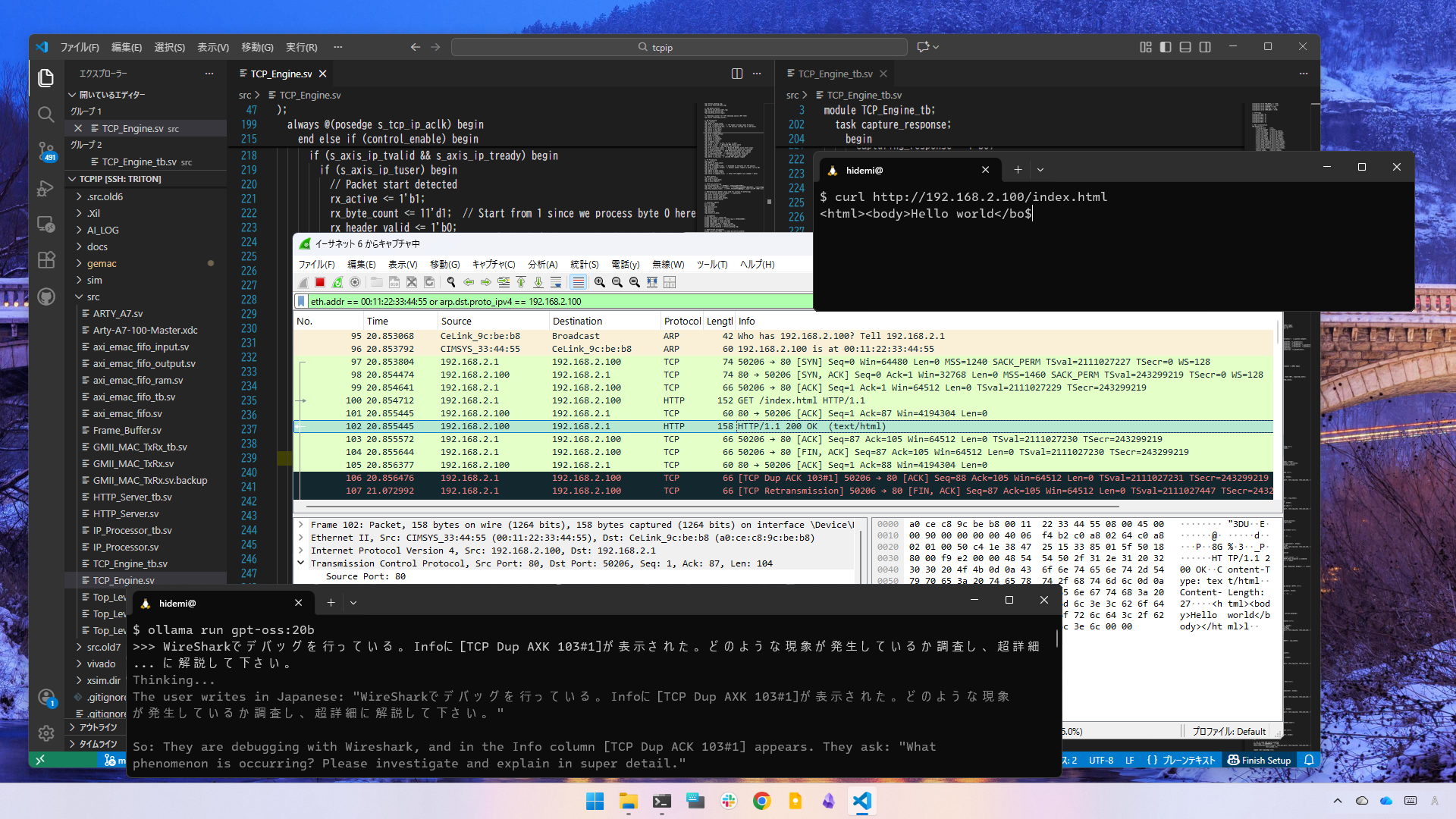

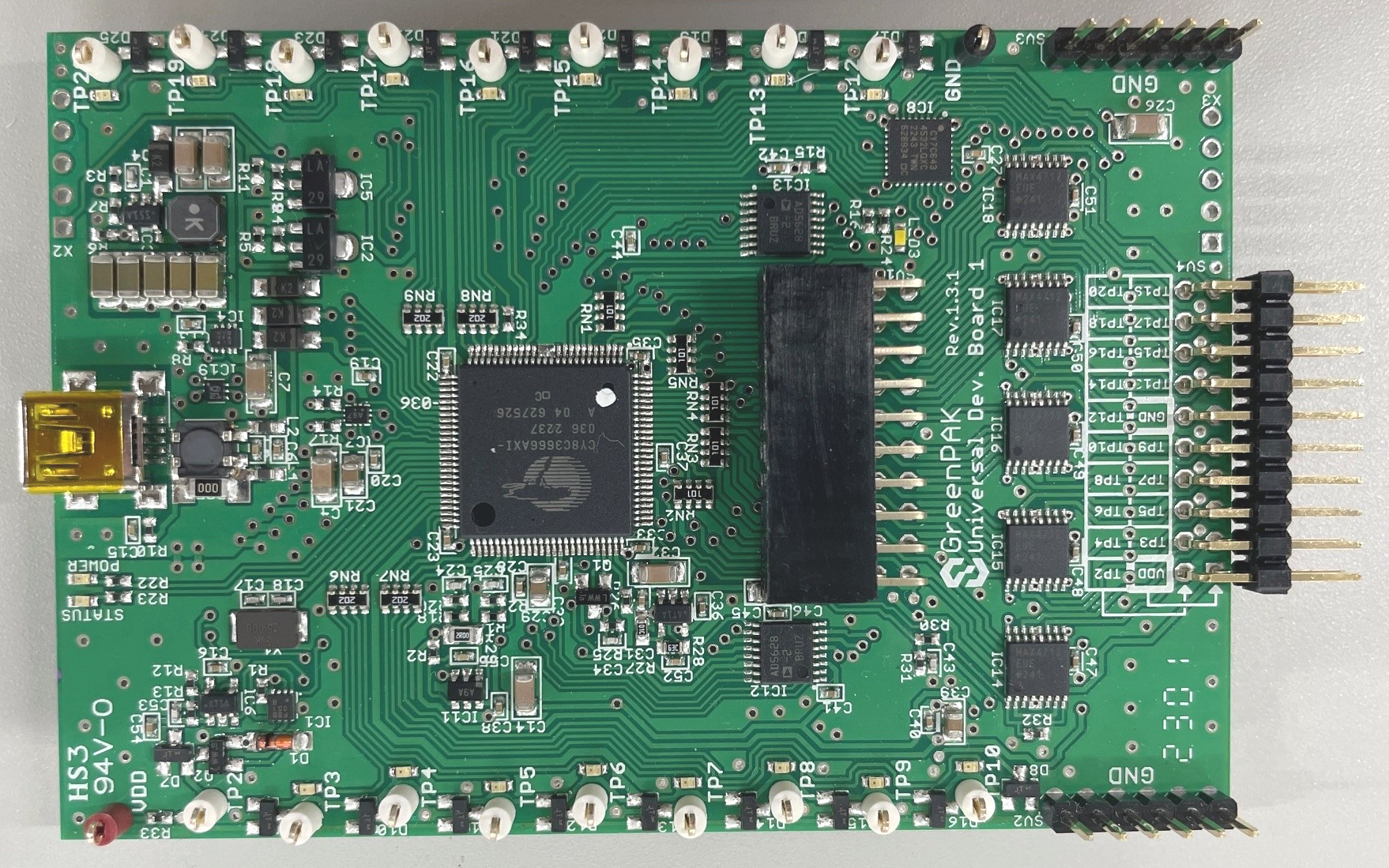

●創刊主旨 2023年リニューアル創刊!

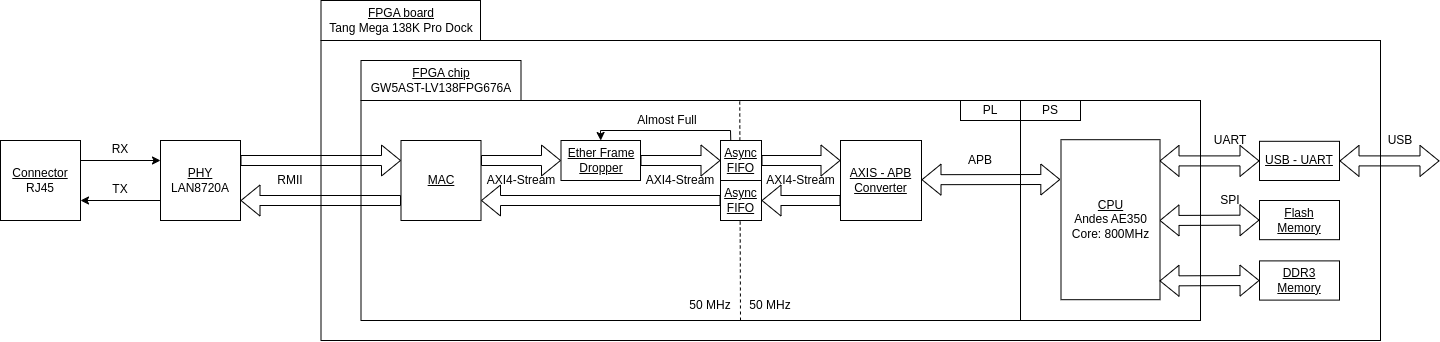

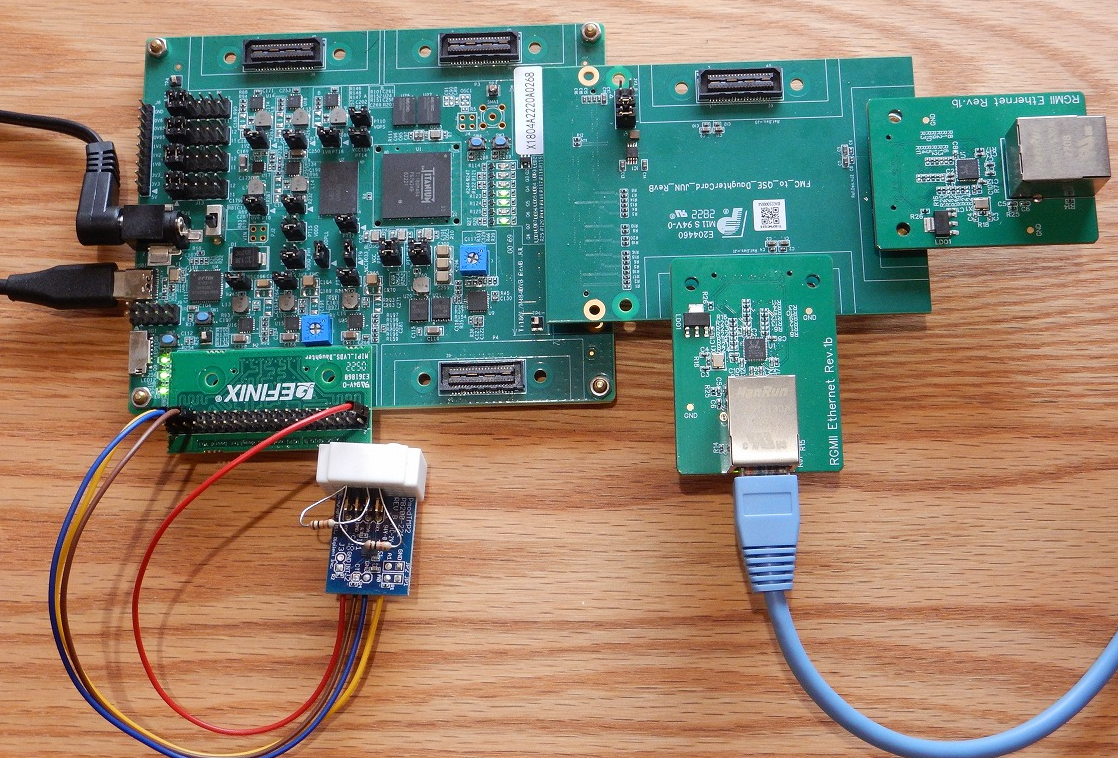

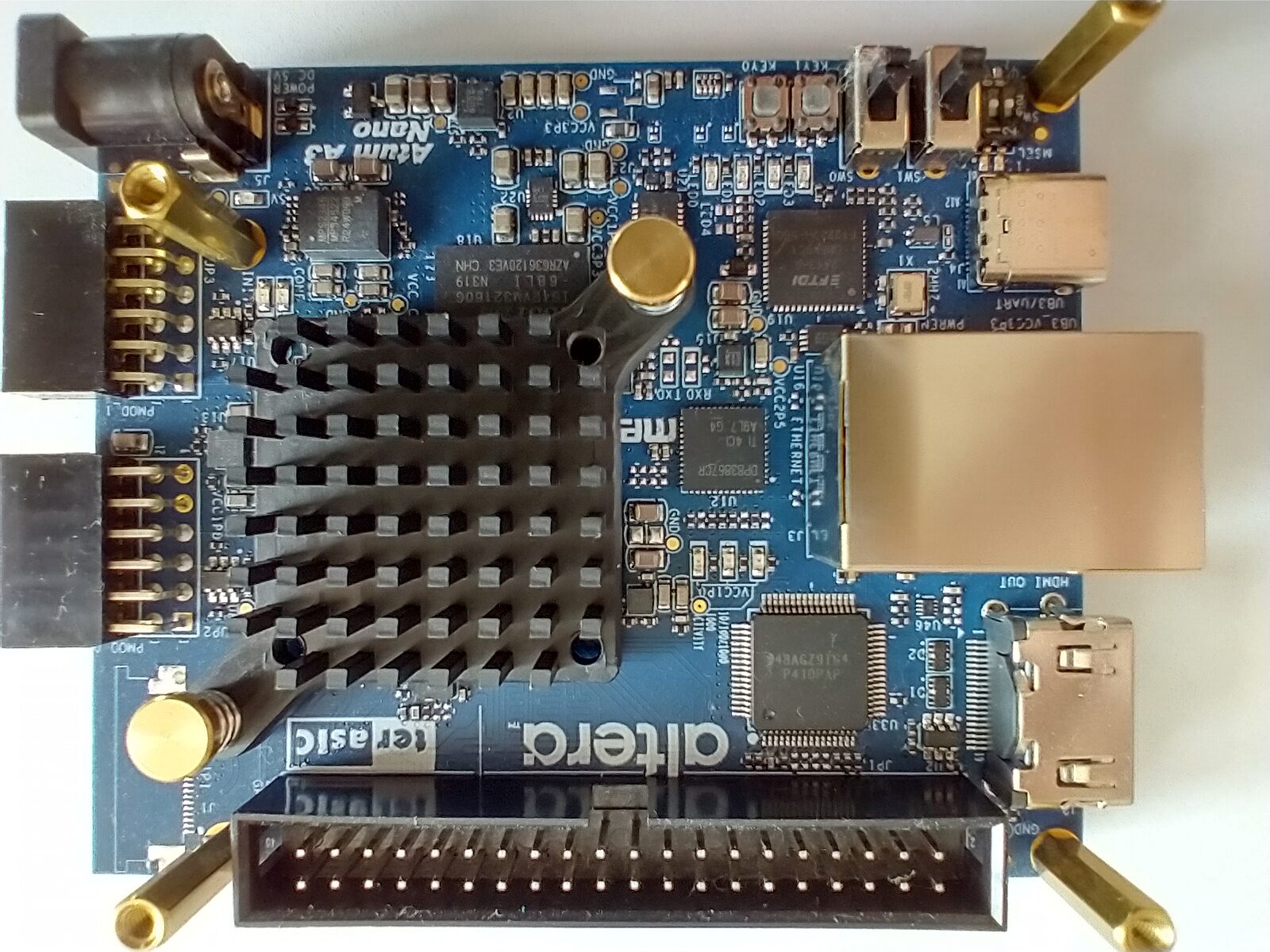

FPGAが世の中に登場して30数年が経ちました.当初は価格も高くゲート規模も小さかったものが,半導体製造技術の進歩により,低価格化,大容量化,高機能化が進みました.従来,ASICなどの試作開発やCPU周辺のグルーロジックをまとめる用途で使われていたFPGAは,大容量化により周辺機能をどんどん取り込み,SoC(System on a chip)を実現できるレベルに達しました.そして今日,ARMコアを内蔵したFPGAが登場しました.デュアルコア/800MHzというハイパワー・プロセッサを内蔵し,ユーザの手元でSoCが1個からでも実現できる夢のデバイスとなりました.

2013年に創刊したFPGAマガジンは,ユニークでオリジナリティのある機器を設計するエンジニアを全面的に支援することを目的に,大容量化,高機能化したFPGAをいかに使いこなすかをハードウェア/ソフトウェアの両面から,応用事例を交え実践的に解説してきました.2018年に休刊していたのですが,2023年,読者の要望を受けて,Interface誌別冊付録としてリニューアル創刊しました.