Tang Primer 25K(Sipeed)のオプションとしてSDRAMモジュールが販売されている(Aliexpressで2000円程度).このモジュールは,40ピンのピンヘッダ(2.54mm)を介して,Tang Primer 25K本体と接続する.

ちなみに,このモジュールには,v1.2 と v1.3(ちょっと小さくなってる) が存在する(Schematicがあるので,v1.1も有った?).

MiSTer SDRAM V3.0と似ているが,少しピン配列が違う旨,公式ページにも注意書きがある.

●サンプル・プロジェクトで動作確認

サンプル・プロジェクトがGitHubにある.Lichee Tangと書いてあるが,どうやらTang Primer 25Kでも動くようである.もともとは,AnlogicのFPGAを搭載したボード Lichee Tang Primer用のデザインだったようである(詳細不明).

Gowin IDEのプロジェクトが1つだけ入っているので,それを開く.

変更点は次の通り.

▲デバイス

「Project」-「Set Device」とクリックし,GW5A-LV25MG121NESを選択する.

▲Dual Purpose Pin

「Project」-「Configuration」とクリックし,Place&Routeの中のDual Purpose Pinを開く.JTAG以外全部チェックを入れる.

▲HDL

「Project」-「Configuration」とクリックし,SynthesizeのGeneralを開く.Verilog Language:でSystem Verilog 2017を選択する.

▲TA

Timing Constraint Editorを開く.Path-False Pathをクリックする.2行設定がされているが,1行目をダブルクリックしてダイアログを開く.

Fromの中の,print_state_1_s0 を print_state_1_s1 に変える.

Toの中の,print_state_1_s0 を print_state_1_s1 に変える.

●合成と実行

合成して書き込んでテスト.

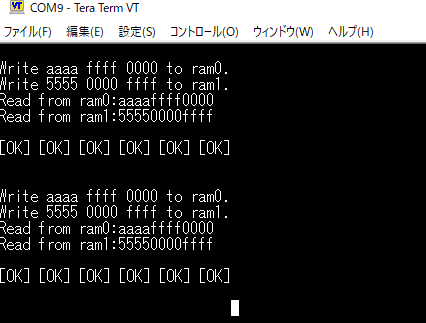

サンプル・デザインでは,USB-シリアルで結果が出力されるので,ホストのTera Termで観測する. 設定は,115200bps,8N1

Tang Primer 25Kのボード上にあるS1スイッチを押すと,UARTに出力される.

SDRAMモジュールを接続するときは,向きに注意!

大事なことなのでもう一回言います.向きに注意です(間違うと 壊れるっぽい).

参考文献

(1)Gowin タイミング制約 ユーザーガイド SUG940-1.8.2J, 2024-10-25