[特別版No.5 特集第1部]

ターゲットボード:Arty A7(Digilent)

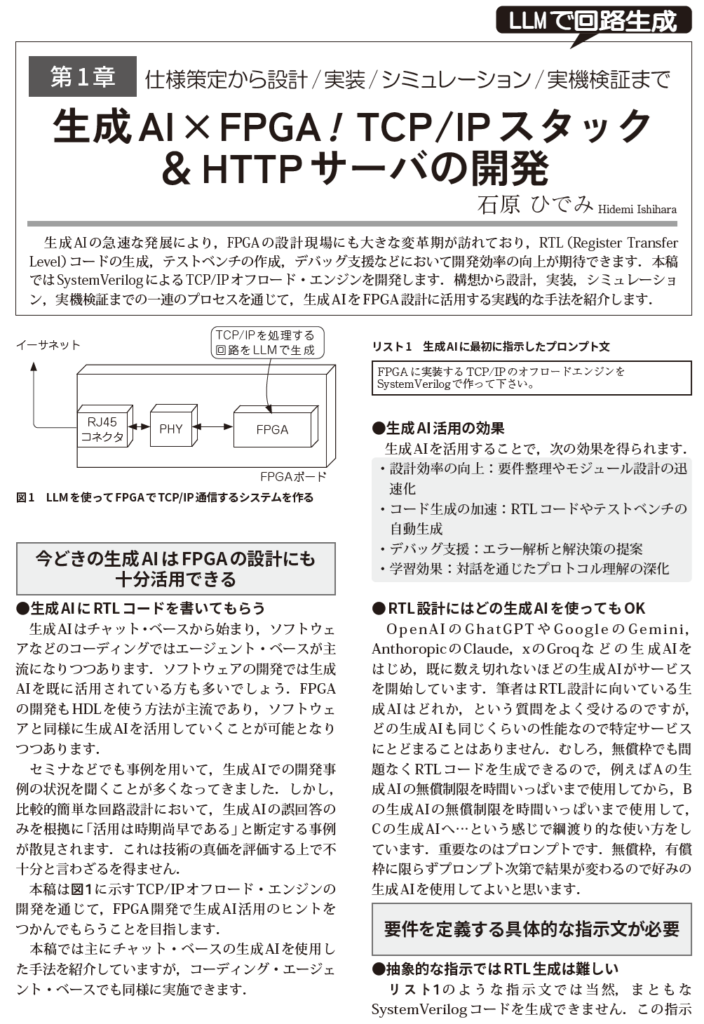

TCP/IP通信を,LLMを使って回路実装します.

CPU用ソフトウェアの生成に比べて,ディジタル回路を生成するのは苦手なLLMですが,繰り返し指示することで正しい回路を生成するように誘導できます.

TCPの処理は再送制御などが煩雑であり,回路として実装するのは簡単ではありません.しかし,外部とのI/FとしてEtherは汎用的であり,SmartNICなど低遅延を必要とするアプリケーションでも必要とされていることから,IPを利用して実装している方も多いでしょう.

FPGAへのTCP実装では,アプリケーションに応じてバッファの量などを調整したい場合もあります.独自のTCP実装において,それらをスケール出来れば とても有用な実装技術となりそうです.