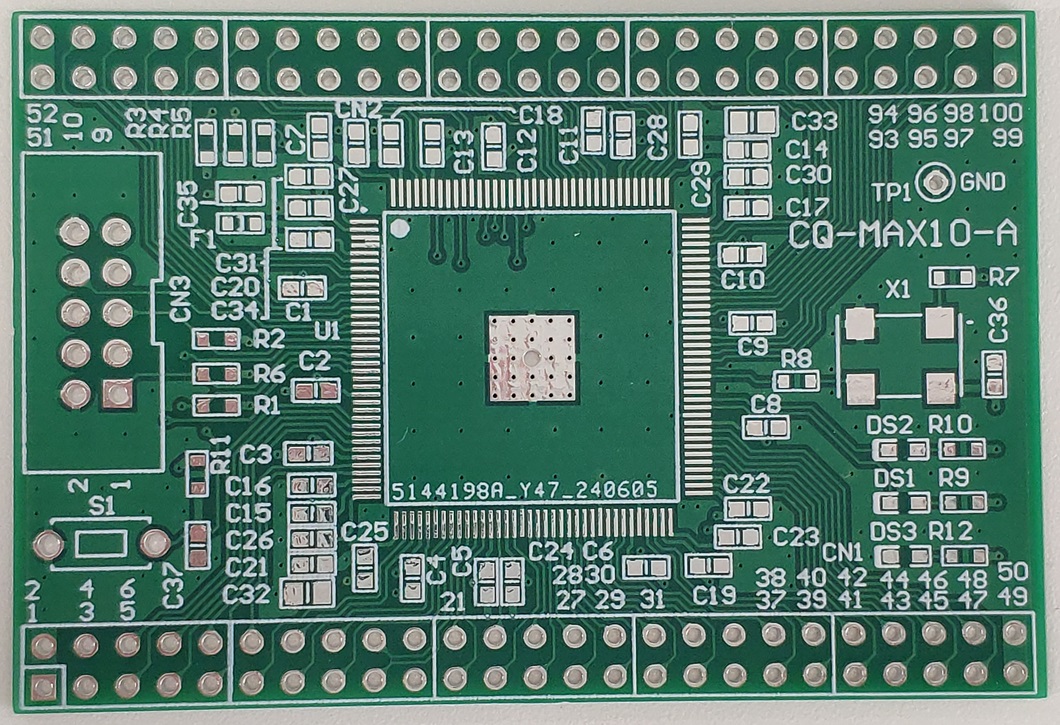

MAX10を搭載するFPGAボードを設計する

AlteraのFPGAであるMAX10を搭載するFPGAボードを自作します.生基板やガーバーデータも配布します. FPGAボードの自作を通して,ツールを利用して電源回路を設計したり,必要なパスコンを概算したりといった基板設計のポイントを説明します.アルテラのFPGAであるMAX10のラインアップには,手はんだでも実装可能な144ピンQFPパッケージがあります.本稿ではこれを使って独自のFPGAボードを作ります.ガーバ・データや生基板も配布するので,パスコンの違いによる特性の変化などを実験で確かめることもできます.

2件のコメント

2024年3月15日